掌握八大電路設(shè)計技巧,邁向卓越集成電路設(shè)計之路

在集成電路設(shè)計領(lǐng)域,專業(yè)素養(yǎng)的提升往往源于對關(guān)鍵技巧的深入理解和靈活運(yùn)用。無論是模擬電路、數(shù)字電路還是混合信號設(shè)計,精湛的技巧都能顯著提高設(shè)計效率、優(yōu)化性能并規(guī)避潛在風(fēng)險。以下是八個能夠大大提升你專業(yè)素養(yǎng)的電路設(shè)計核心技巧。

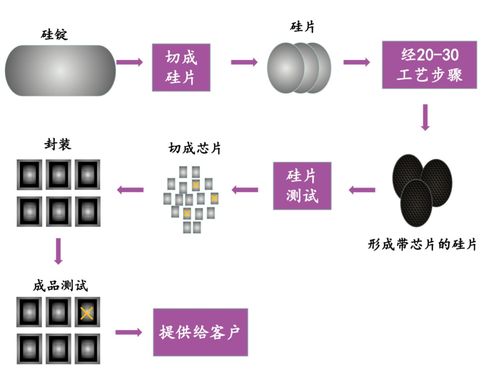

第一,深刻理解器件模型與工藝角。優(yōu)秀的IC設(shè)計師從不將晶體管視為理想開關(guān)。你必須深入理解SPICE模型參數(shù)(如Vth、Cox、遷移率),并熟練掌握在典型(TT)、快(FF)、慢(SS)等工藝角下進(jìn)行仿真分析。這能確保你的電路在制造工藝波動下依然穩(wěn)健工作,是保證芯片良率的基礎(chǔ)。

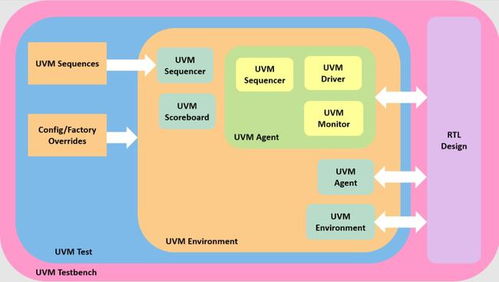

第二,模塊化與層次化設(shè)計思維。將復(fù)雜系統(tǒng)分解為功能清晰、接口明確的子模塊。這不僅使設(shè)計、仿真和調(diào)試更易管理,也便于團(tuán)隊協(xié)作和IP復(fù)用。清晰的層次結(jié)構(gòu)能讓你的設(shè)計思路像建筑藍(lán)圖一樣一目了然。

第三,精打細(xì)算的功耗管理。從系統(tǒng)架構(gòu)到晶體管級,功耗始終是核心考量。掌握多電壓域設(shè)計、電源門控、時鐘門控、動態(tài)電壓頻率縮放(DVFS)等低功耗技術(shù)。學(xué)會分析靜態(tài)功耗與動態(tài)功耗的來源,并在速度、面積和功耗之間做出最佳權(quán)衡。

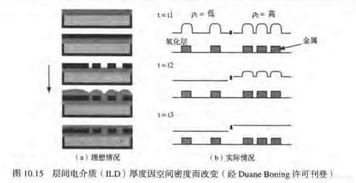

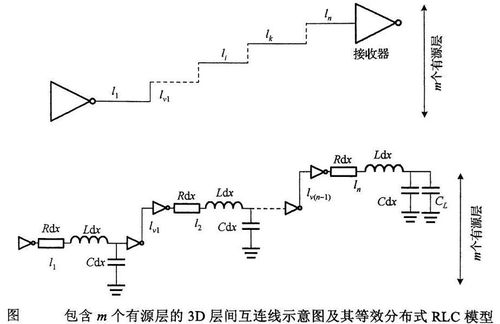

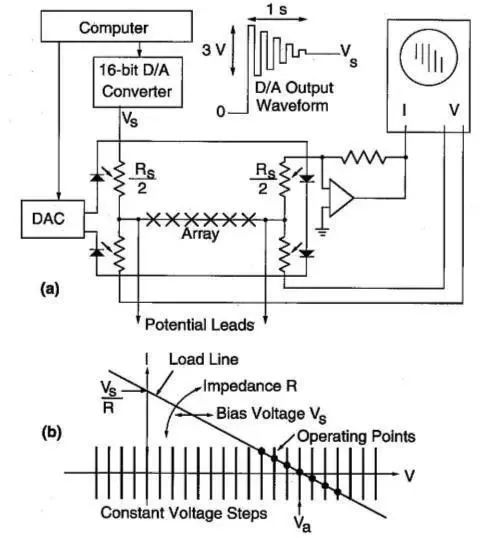

第四,擁抱仿真與驗(yàn)證的全面性。依賴單一仿真結(jié)果是危險的。建立一個覆蓋直流工作點(diǎn)、交流小信號、瞬態(tài)、蒙特卡洛、工藝角、溫度掃描以及后仿真的完整驗(yàn)證流程。特別是后仿真,它能揭示版圖寄生參數(shù)(如寄生電阻、電容)帶來的性能影響,是流片前最后的關(guān)鍵檢查。

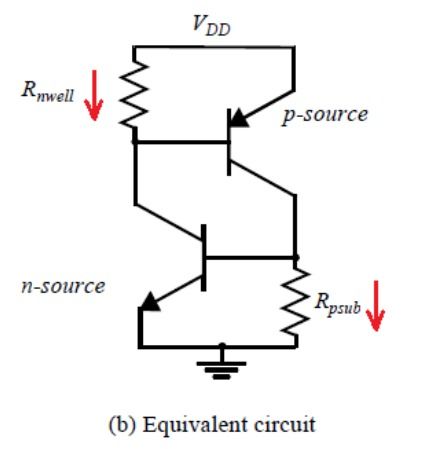

第五,將信號完整性與可靠性融入設(shè)計。關(guān)注串?dāng)_、地彈、電源噪聲、電遷移(EM)、靜電放電(ESD)和閂鎖效應(yīng)(Latch-up)等問題。在版圖階段就要有意識地通過屏蔽、隔離、增加保護(hù)環(huán)、合理規(guī)劃電源網(wǎng)格等方法來提升電路的魯棒性。

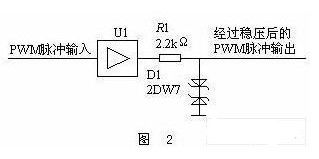

第六,掌握時序收斂的關(guān)鍵。對于數(shù)字電路,時序就是生命線。你需要精通靜態(tài)時序分析(STA)的概念,理解建立時間、保持時間、時鐘偏差、時鐘抖動。合理設(shè)計時鐘樹,并利用緩沖器插入、邏輯重組、管線化等技巧來滿足苛刻的時序要求。

第七,培養(yǎng)對噪聲與匹配的敏銳直覺。在模擬和混合信號設(shè)計中,噪聲(熱噪聲、閃爍噪聲)和器件失配是性能的主要限制因素。學(xué)會計算等效輸入噪聲,并運(yùn)用共質(zhì)心、交叉耦合等版圖技術(shù)來改善匹配性,這對差分對、電流鏡、數(shù)據(jù)轉(zhuǎn)換器等電路至關(guān)重要。

第八,學(xué)會與版圖工程師高效協(xié)作。電路設(shè)計并非止于原理圖。理解版圖設(shè)計的基本約束和最佳實(shí)踐(如匹配、對稱、走線寬度、天線效應(yīng)),能用清晰的標(biāo)注和文檔指導(dǎo)版圖工作。積極參與版圖后的仿真驗(yàn)證,形成設(shè)計-版圖-驗(yàn)證的閉環(huán)。

總而言之,集成電路設(shè)計是一門融合了理論深度與工程實(shí)踐的藝術(shù)。熟練掌握這八大技巧,意味著你不僅能設(shè)計出功能正確的電路,更能創(chuàng)造出高性能、高可靠、可制造性強(qiáng)的芯片產(chǎn)品。持續(xù)學(xué)習(xí)、勤于實(shí)踐、注重細(xì)節(jié),你的專業(yè)素養(yǎng)必將在此過程中得到質(zhì)的飛躍,從而在激烈的行業(yè)競爭中脫穎而出。

如若轉(zhuǎn)載,請注明出處:http://www.aalaton.cn/product/62.html

更新時間:2026-01-21 22:38:12